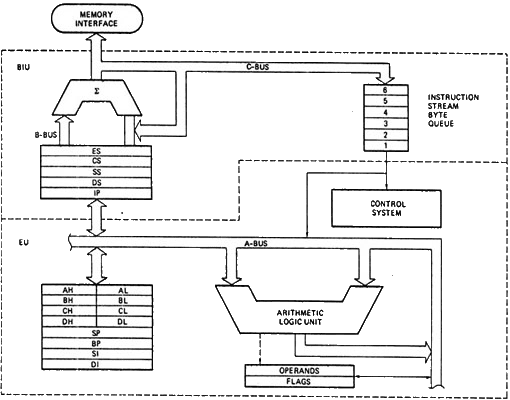

Working of EU and BIU of 8086 Microprocessor: The 8086 microprocessor is comprised of two key execution units: the Execution Unit (EU) and the Bus Interface Unit (BIU). Each plays a distinct role in the overall operation of the processor. These units work together to execute instructions and manage data transfer between the microprocessor and memory or peripherals.

Execution Unit (EU):

- Function:

- The EU is responsible for executing instructions. It performs arithmetic and logic operations on data as directed by the instructions in the program.

- It includes the Arithmetic and Logic Unit (ALU) that performs mathematical and logical operations, as well as general registers to store data during computation.

- Registers:

- The EU contains various registers, including general-purpose registers like AX, BX, CX, and DX, which are used for data manipulation.

- The instruction pointer (IP) register keeps track of the address of the next instruction to be executed.

- Instruction Execution:

- The EU fetches instructions from memory using the BIU.

- Once an instruction is fetched, the EU decodes it to determine the operation to be performed and fetches any required operands.

- The ALU then executes the operation, and the result is stored in the appropriate registers.

Bus Interface Unit (BIU):

- Function:

- The BIU is responsible for managing the flow of data between the microprocessor and external devices, such as memory and I/O devices.

- It provides the necessary control signals for the data bus and address bus.

- Segmentation:

- The 8086 uses a divided memory style. The BIU manages the division of memory addresses, putting together a 16-bit part of the address from a register with a 16-bit shift to create a 20-bit actual address.

- Address Generation:

- The BIU generates the physical memory address for fetching instructions and data. It combines the information of the segment registers (CS, DS, SS, ES) with the offset values to create the complete memory address.

- Bus Control:

- The BIU manages the control signals for the system buses, including the address bus, data bus, and control bus.

- It generates signals to control the flow of data between the microprocessor and memory or peripherals.

Interaction Between EU and BIU:

- Instruction Fetch:

- The BIU fetches instructions from memory and places them in the instruction queue.

- The EU then takes instructions from the queue, decodes them, and executes the corresponding operations.

- Data Transfer:

- When data needs to be transferred between the microprocessor and memory or peripherals, the BIU handles the address generation and control signals.

- The EU, on the other hand, manages the actual execution of instructions that involve data manipulation (Handling or controlling).

- Execution Flow:

- The BIU and EU cooperate, with the BIU managing the external data and address pathways while the EU carries out the real execution of instructions.

- The BIU ensures a smooth flow of data and instructions between the microprocessor and the external environment.

In summary, the Execution Unit (EU) of the 8086 is responsible for executing instructions, performing arithmetic and logic operations, and managing registers. The Bus Interface Unit (BIU) is responsible for managing data transfer between the microprocessor and external devices, handling address generation, and controlling the system buses. Together, these units allow the 8086 to fetch, decode, and execute instructions in a coordinated manner.